# **TS75C96**

# V.32, V.29, V.27ter, V.22bis, V.22, V.23, BELL 212A, BELL 103 MODEM CHIP SET

**ADVANCE DATA**

- CCITT V.32, V.22bis, V.22, V.21, V.23, Bell 212A, Bell 103 COMPATIBLE MODEM CHIP SET

- CCITT V.29, V.27ter FOR FAX APPLICATIONS

- INTEGRATED IMPLEMENTATION ON THREE DSP AND THREE MAFE CHIPS

- FULL DUPLEX OPERATION FROM 9600 TO 300bps

- FULL IMPLEMENTATION OF THE V.32 AND V.22bis HANDSHAKE

- V.29/4800bps AND V.27ter SHORT TRAIN SE-QUENCES

- DYNAMIC RANGE: 43dB

- TWO SATELLITE HOPS AND FREQUENCY OFFSET CAPABILITIES (10Hz) FOR THE FAR END ECHO CANCELLER IN V.32 MODE

- TRELLIS ENCODING AND VITERBI DECOD-ING

- 12.5% ROLL-OFF RAISED COSINE TRANS-MITTER PULSE SHAPING

- HIGH PERFORMANCE PASSBAND FRAC-TIONALLY SPACED ADAPTIVE EQUALIZER

- SIGNAL QUALITY MONITORING

- PARALLEL INTERFACE TO STANDARD MI-CROPROCESSORS

- SERIAL DATA TRANSMIT CAPABILITY

- V.14 AND V.54 IMPLEMENTATION

- LOW POWER MODE AVAILABLE (PLCC)

- BIT RATE DATA CLOCKS PROVIDED FOR SYNCHRONOUS DATA TRANSFER

- FULL DIAGNOSTIC CAPABILITY

- DTMF GENERATION

- CALL PROGRESS TONE DETECTION

- PROGRAMMABLE FILTERS FOR "AUTO-BAUD" IMPLEMENTATION

- SOFTWARE LICENSE AND DEVELOPMENT TOOLS AVAILABLE FOR EASY CUSTOMIZA-TION

- TOTAL POWER CONSUMPTION BELOW 1.5W

#### **DESCRIPTION**

The SGS-THOMSON Microelectronics TS75C96 chip set is a highly integrated modem engine, which can operate in full duplex from 9600 to 300bps. The modem hardware consists of three analog front end (MAFE) chips, three DSP processor chips and additional memory chips plus the V.14 serial output converter. The three SGS-THOMSON analog front end chips (TS68950/1/2) are the transmit interface, the receive interface and the clock generator respectively. The modem signal processing functions are implemented on three ST18930 programmable digital signal processors.

February 1995 1/47

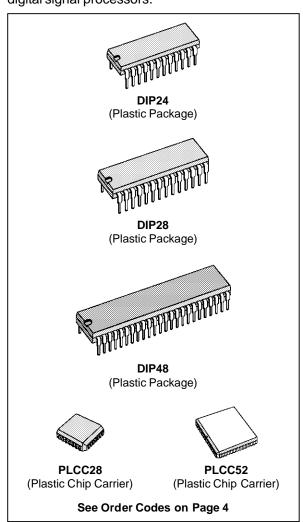

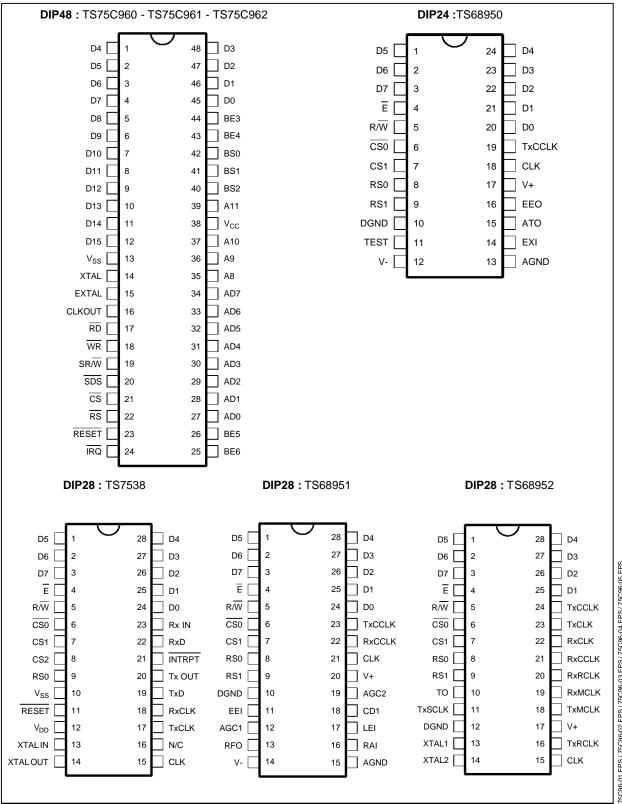

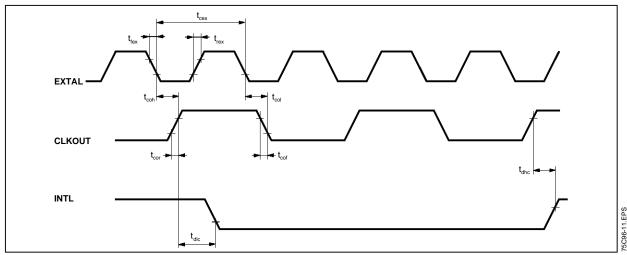

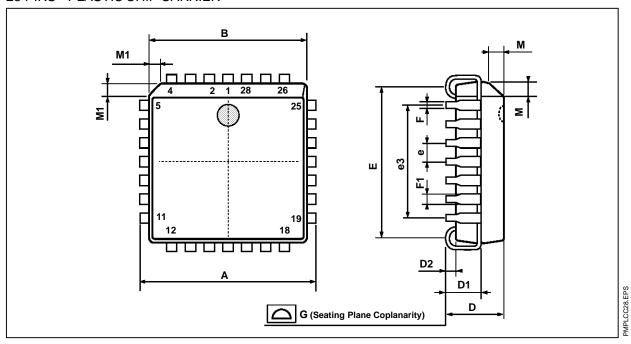

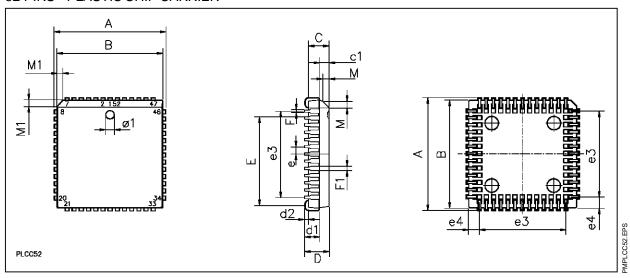

#### **PIN CONNECTIONS**

#### **PIN CONNECTIONS**

## **ORDER CODES**

| Part Number  | Temperature Range | Package |

|--------------|-------------------|---------|

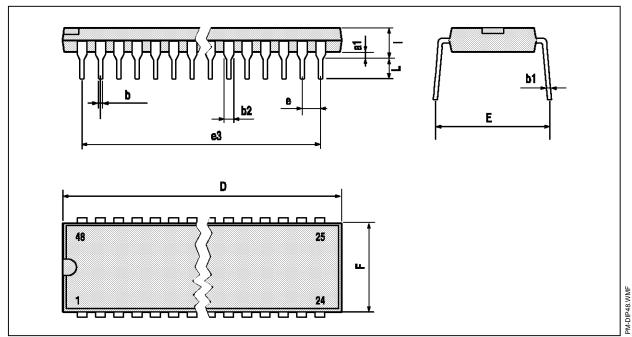

| TS75C960CP-S | 0°C to +70°C      | DIP48   |

| TS75C961CP-S | 0°C to + 70°C     | DIP48   |

| TS75C962CP-S | 0°C to +70°C      | DIP48   |

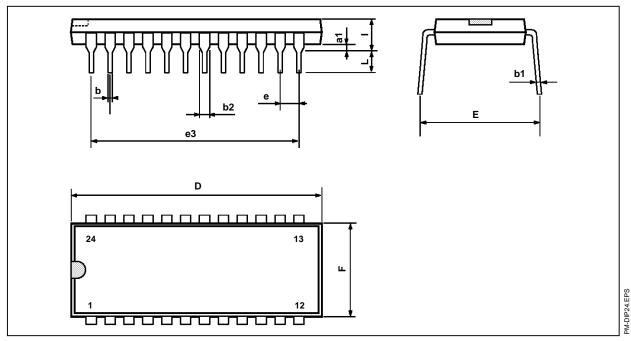

| TS68950CP    | 0°C to +70°C      | DIP24   |

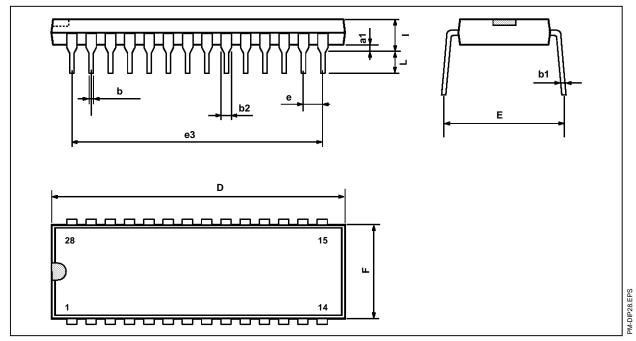

| TS68951CP    | 0°C to +70°C      | DIP28   |

| TS68952CP    | 0°C to + 70°C     | DIP28   |

| Part Number   | Temperature Range | Package |

|---------------|-------------------|---------|

| TS7538CP      | 0°C to + 70°C     | DIP28   |

| TS75C960CFN-S | 0°C to + 70°C     | PLCC52  |

| TS75C961CFN-S | 0°C to + 70°C     | PLCC52  |

| TS75C962FN-S  | 0°C to + 70°C     | PLCC52  |

| TS68950CFN    | 0°C to + 70°C     | PLCC28  |

| TS68951CFN    | 0°C to + 70°C     | PLCC28  |

Description

96-01.TBL

## **PIN DESCRIPTION**

## SYSTEM INTERFACE

Pin Name | Type | Signal Name

| TS75C961 (DSF | TS75C961 (DSP # 1 Transmitter and Handshake) |        |                                                                                                                        |  |  |  |

|---------------|----------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AD0AD7        | I/O                                          | D0HD7H | System Data Bus: these lines are used for data transfer between the TS75C96 mailbox and the host processor             |  |  |  |

| CS            | ı                                            | CSL    | Chip Select: this input is asserted when the TSC75C96 is to be accessed by the host processor                          |  |  |  |

| RS            | I                                            | RSL    | Register Select : this signal is used to control the data transfers between the host processor and the TS75C96 mailbox |  |  |  |

| SDS           | I                                            | DSL    | System Data Strobe: synchronizes the transfer between the TS75C96 mailbox and the host processor                       |  |  |  |

| SR/W          | I                                            | RWL    | System Read/Write: control signal for the TSC75C96 mailbox operation                                                   |  |  |  |

| ĪRQ           | 0                                            | INTL   | Interrupt Request : signal sent to the host processor to access the TS75C96 mailbox                                    |  |  |  |

| RESET         | ı                                            | RSTI 1 | Master Reset (All DSP's RESET connected to this pin)                                                                   |  |  |  |

## DATA INTERFACE

| Pin Name | Туре | Signal Name | Description          |

|----------|------|-------------|----------------------|

| TS7538   |      |             |                      |

| TxD      | 1    | TxD         | Serial Transmit Data |

| RxD      | 0    | RxD         | Serial Receive Data  |

## **ANALOG INTERFACE**

| Pin Name                               | Туре     | Signal Name   | Description                         |

|----------------------------------------|----------|---------------|-------------------------------------|

| TS68950 (Analog Front-end Transmitter) |          |               |                                     |

| ATO                                    | 0        | ATO           | Analog Transmit Output              |

| TS68951 (Analo                         | g Front- | end Receiver) |                                     |

| RAI                                    | I        | RAI           | Receive Analog Input                |

| LEI                                    | I        | LEI           | Local Echo Input. Must be grounded. |

## **CLOCK INTERFACE**

| Pin Name       | Type     | Signal Name    | Description                                                                                                                           |

|----------------|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| TS68952 (Analo | g Front- | end Clock Gene | rator)                                                                                                                                |

| TxCLK          | 0        | TxCLK          | Transmit Bit Clock                                                                                                                    |

| TxRCLK         | 0        | TxRLCK         | Transmit Baud Clock                                                                                                                   |

| TxCCLK         | 0        | TxCCLK         | Transmit Conversion Clock                                                                                                             |

| TxMCLK         | 0        | TxMCLK         | Transmit Multiplex Clock                                                                                                              |

| RxCLK          | 0        | RxCLK          | Receive Bit Clock                                                                                                                     |

| RxRCLK         | 0        | RxRCLK         | Receive Baud Clock                                                                                                                    |

| RxCCLK         | 0        | RxCCLK         | Receive Conversion Clock                                                                                                              |

| RxMCLK         | 0        | RxMCLK         | Receive Multiplex Clock                                                                                                               |

| TxSCLK         | 1        | TxSCLK         | Transmit Synchro Clock: can be used to synchronize the transmitter on an external bit clock provided by the RS232C (or V.24) junction |

5C96-02.TBL

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                                   | Value                                                    | Unit |

|---------------------|---------------------------------------------|----------------------------------------------------------|------|

| TS75C960/1/         | /2                                          |                                                          |      |

| V <sub>CC</sub> (1) | Supply Voltage                              | -3.0, 7.0                                                | V    |

| V <sub>IN</sub> (1) | Input Voltage                               | -3.0, 7.0                                                | V    |

| T <sub>amb</sub>    | Operating Temperature                       | 0, + 70                                                  | °C   |

| T <sub>stg</sub>    | Storage Temperature                         | -55, <b>+</b> 150                                        | °C   |

| TS68950/1/2         |                                             |                                                          |      |

|                     | Supply Voltage between V + and AGND or DGND | -0.3, +7                                                 | V    |

|                     | Supply Voltage between V – and AGND or DGND | -7, +0.3                                                 | V    |

|                     | Voltage between AGND and DGND               | -0.3, +0.3                                               | V    |

|                     | Digital Input Voltage                       | DGND -0.3, V <sub>CC</sub> <sup>+</sup> + 0.3            | V    |

|                     | Digital Output Voltage                      | DGND -0.3, V <sub>CC</sub> <sup>+</sup> + 0.3            | V    |

|                     | Digital Output Current                      | -20, + 20                                                | mA   |

|                     | Analog Input Voltage                        | V <sub>CC</sub> -0.3, V <sub>CC</sub> <sup>+</sup> + 0.3 | V    |

|                     | Analog Output Voltage                       | V <sub>CC</sub> -0.3, V <sub>CC</sub> <sup>+</sup> + 0.3 | V    |

|                     | Analog Output Current                       | -10, + 10                                                | mA   |

| T <sub>oper</sub>   | Operating Temperture                        | 0, + 70                                                  | °C   |

| T <sub>stg</sub>    | Storage Temperture                          | <b>–</b> 65, <b>+</b> 150                                | °C   |

Note: 1. With respect to Vss.

Stresses above those hereby listed may cause permanent damage to the device. The ratings are stress ones only and functional operation of the device at these or any conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Standard MOS circuits handling procedure should be used to avoid possible damage to the device.

## **DC ELECTRICAL CHARACTERISTICS** (DGND = AGND = 0V)

| Symbol           | Parameter                                                                                     | Min.               | Тур. | Max. | Unit |

|------------------|-----------------------------------------------------------------------------------------------|--------------------|------|------|------|

| DIGITAL SUF      | PPLY ( $V_{CC} = 5.0V \pm 10\%$ , $V_{SS} = 0V$ , $T_{amb} = 0$ to $+70^{\circ}$ C, unless of | otherwise specific | ed)  |      |      |

| Vcc              | Supply Voltage                                                                                | 4.5                | 5    | 5.5  | V    |

| V <sub>IL</sub>  | Input Low Voltage                                                                             | -0.3               |      | 0.8  | V    |

| $V_{IH}$         | Input High Voltage                                                                            | 2.4                |      | Vcc  | V    |

| li               | Input Extal Current                                                                           | -50                |      | +50  | μΑ   |

| V <sub>OH</sub>  | Output High Voltage (I <sub>load</sub> =-300 μA)                                              | 2.7                |      |      | V    |

| V <sub>OL</sub>  | Output Low Voltage (I <sub>load</sub> =3.2 mA)                                                |                    |      | 0.5  | V    |

| P <sub>D</sub>   | Total Power Dissipation                                                                       |                    | 1.0  |      | W    |

| C <sub>in</sub>  | Input Capacitance                                                                             |                    | 10   |      | pF   |

| I <sub>TSI</sub> | Three State (Off State) Input Current                                                         | -20                |      | -20  | mA   |

| ANALOG SU        | PPLY                                                                                          | ·                  |      | •    |      |

| V <sup>+</sup>   | Positive Power Supply                                                                         | 4.75               |      | 5.25 | V    |

| V <sup>-</sup>   | Negative Power Supply                                                                         | -5.25              |      | 4.75 | V    |

| l <sup>+</sup>   | Positive Supply Current                                                                       |                    |      | 35   | mA   |

| -                | Negative Supply Current                                                                       | -35                |      |      | mA   |

Note: Case Temperature T must be mantained below 100°C.

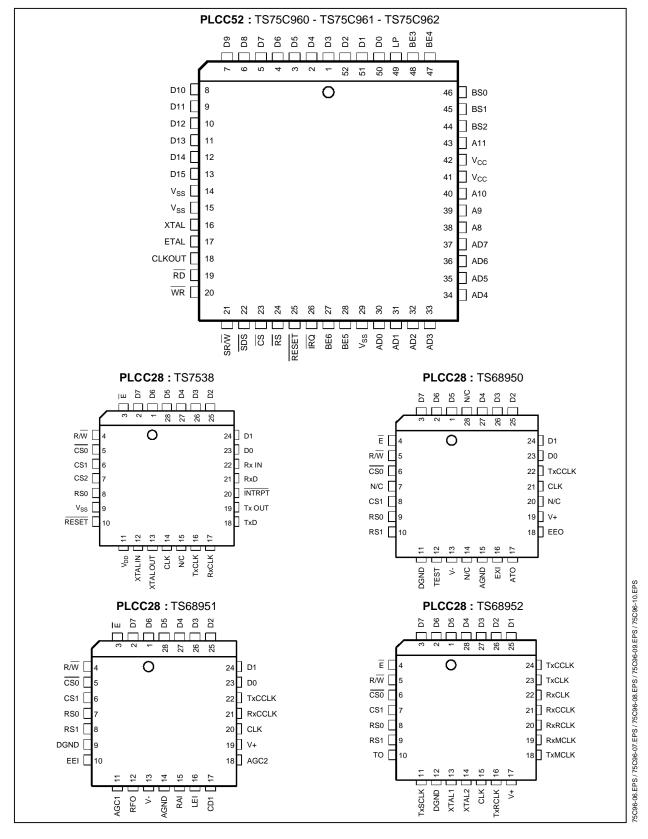

## **AC ELECTRICAL SPECIFICATIONS**

## **CLOCK AND CONTROL PINS TIMINGS**

$(V_{CC} = 5.0V \pm 10\%, T_{amb} = 0 \text{ to} + 70^{\circ}\text{C}, \text{ see Figure 1 - Output Load} = 50pF + DC \text{ characteristics I load Reference Levels}: V_{IL} = 0.8V, V_{IH} = 2.4V, V_{OL} = 1.4V, V_{OH} = 2.4V - t_r, t_f \le 5ns \text{ for input signal})$

| Symbol           | Parameter                                                      | Test Conditions | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------------|-----------------|------|------|------|------|

| t <sub>cex</sub> | External Clock Cycle Time T <sub>C</sub> =2 x t <sub>cex</sub> |                 | 40   |      | 43.4 | ns   |

| t <sub>fex</sub> | External Clock Fall Time                                       |                 |      |      | 5    | ns   |

| t <sub>rex</sub> | External Clock Rise Time                                       |                 |      |      | 5    | ns   |

| t <sub>coh</sub> | EXTAL to CLKOUT High Delay                                     |                 |      | 25   |      | ns   |

| t <sub>col</sub> | EXTAL to CLKOUT Low Delay                                      |                 |      | 25   |      | ns   |

| t <sub>cor</sub> | CLKOUT Rise Time                                               |                 |      |      | 10   | ns   |

| t <sub>cof</sub> | CLKOUT Fall Time                                               |                 |      |      | 10   | ns   |

| t <sub>dlc</sub> | CLKOUT to Control Output Low (INTL)                            |                 |      |      | 30   | ns   |

| t <sub>dhc</sub> | CLKOUT to Control High (INTL)                                  |                 |      |      | 30   | ns   |

## TS7538 CLOCK GENERATOR

| Symbol  | Parameter                           | Test Conditions                                                                  | Min.      | Тур.      | Max.      | Unit |

|---------|-------------------------------------|----------------------------------------------------------------------------------|-----------|-----------|-----------|------|

| CRYSTAL | OSCILLATOR INTERFACE (Vcc = 5V +10% | $V_{\text{SS}} = 0 \text{V}  T_{\text{amb}} = 0 \text{ to } 70^{\circ} \text{C}$ | unless of | herwise s | necified) |      |

| VIL              | Low Level Input Voltage        |                                   | -0.3 |     | 0.8      | V  |

|------------------|--------------------------------|-----------------------------------|------|-----|----------|----|

| $V_{IH}$         | High Level Input Voltage       | (all inputs except XTALIN)        | 2.4  |     |          | ٧  |

| V <sub>IHX</sub> | Input High Voltage XTALIN      |                                   |      | 3.5 | $V_{DD}$ | V  |

| I <sub>inX</sub> | Input Laekage Curent on XTALIN | $V_{IN} = 0V$ , $V_{IN} = V_{DD}$ | -10  |     | +10      | μΑ |

CLOCK TIMINGS (V<sub>CC</sub> = 5V  $\pm 10\%$ , T<sub>amb</sub> = 0 to  $70^{\circ}$ C - Output Load = 50pF, DC characteristics load Reference Levels : V<sub>IL</sub> = 0.8V, V<sub>IH</sub> = 3.5V, V<sub>OL</sub> = 0.8V, V<sub>OH</sub> = 2.4V - t<sub>r</sub>, t<sub>f</sub>  $\leq$  5ns for input signals)

| t <sub>CX</sub>                 | XTAL Cycle Time                            |                                | 40 |   |          | ns       |

|---------------------------------|--------------------------------------------|--------------------------------|----|---|----------|----------|

| t <sub>CXW</sub>                | XTAL High or LOW                           |                                | 15 |   |          | ns       |

| t <sub>CXT</sub>                | XTALIN Fall and Rise Time                  |                                |    |   | 5        | ns       |

| t <sub>COD</sub>                | XTAL to CLK and XTALOUT Low and High Delay | XTAL to XTALOUT<br>XTAL to CLK |    |   | 30<br>40 | ns<br>ns |

| t <sub>r</sub> , t <sub>f</sub> | CLK and XTALOUT Fall and Rise Time         |                                |    | 5 |          | ns       |

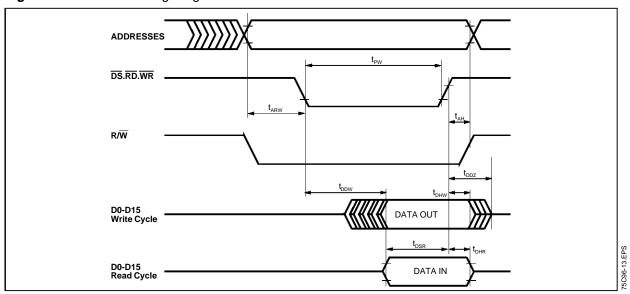

## **LOCAL BUS TIMING**

$(V_{CC} = 5.0V \pm 10\%, T_{amb} = 0 \text{ to} + 70^{\circ}\text{C}, \text{ see Figure 3})$

| Symbol           | Parameter                        |    | Тур. | Max. | Unit |

|------------------|----------------------------------|----|------|------|------|

| t <sub>PW</sub>  | RD, WR, SDS Pulse Widht (1)      | 32 |      | tc/2 | ns   |

| t <sub>AH</sub>  | Address Hold Time                | 5  |      |      | ns   |

| $t_{DDW}$        | Data Delay Time, Write Cycle     |    |      | 40   | ns   |

| $t_{DHW}$        | Data Hold Time, Write Cycle      | 10 |      |      | ns   |

| $t_{DDZ}$        | Data Valid to Z State            |    |      | 40   | ns   |

| tosr             | Data Set-up Time, Read Cycle     | 20 |      |      | ns   |

| t <sub>DHR</sub> | Data Hold Time, Read Cycle       | 5  |      |      | ns   |

| t <sub>ARW</sub> | Address Valid to WR, SDS, RD Low | 20 |      |      | ns   |

**Note:** 1. In multicycle exchanges,  $t_{pw}$  duration is extended by 1, 2, 3 machine cycle lenghts.

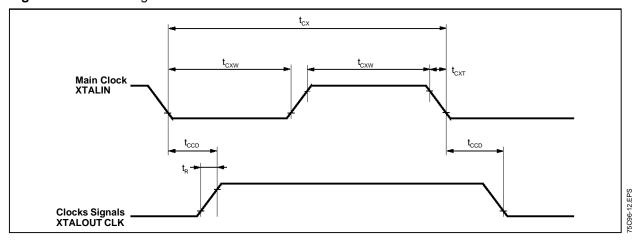

Figure 1 : Clock and Control Pins Timing

Figure 2: Clock Timing

Figure 3: Local Bus Timing Diagram

## AC ELECTRICAL SPECIFICATIONS (continued)

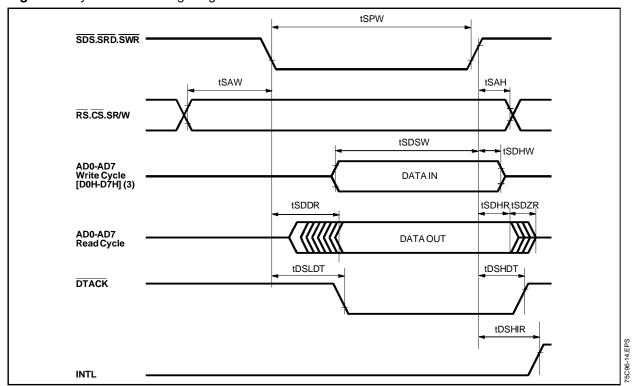

## SYSTEM BUS TIMING

$(V_{CC} = 5.0V \pm 10\%, T_{amb} = 0 \text{ to + } 70^{\circ}\text{C}, \text{ see Figure 4})$

| Symbol             | Parameter                          | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------------|------|------|------|------|

| tspw               | SDS, SRD, SWR Pulse Widht          | 30   |      |      | ns   |

| t <sub>SAW</sub>   | SR/W, CS, RS Sep-up Time15         | 15   |      |      | ns   |

| tsah               | SR/W, CS, RS Hold After SDS High   | 5    |      |      | ns   |

| t <sub>SDSW</sub>  | Data Set-up Time, Write Cycle      | 15   |      |      | ns   |

| t <sub>SDHW</sub>  | Data Hold Time, Write Cycle        | 5    |      |      | ns   |

| tsddr              | Data Delay Time, Read Cycle        |      |      | 25   | ns   |

| t <sub>SDHR</sub>  | Data Hold Time, Read Cycle         | 5    |      |      | ns   |

| t <sub>SDZR</sub>  | DSD, SRD High to Z State           |      |      | 25   | ns   |

| t <sub>DSLDT</sub> | SDS Low to DTACK Low               |      |      | 20   | ns   |

| t <sub>DSHDT</sub> | SDS High to DTACK Desactivated (1) |      |      | 20   | ns   |

| t <sub>DSHIR</sub> | SDS High to IRQ High               |      |      | 800  | ns   |

Notes: 1. DTACK is an open drain output. Test load includes  $R_L = 820\Omega \ V_{DD}$ .

2. This delay depends on programming mode. Its maximum value is  $2T_c + 2$  instruction cycles (see User's Manual).

3. Signal names on Host Processor Interface.

Figure 4: System Bus Timing Diagram

#### **FUNCTIONAL DESCRIPTION**

#### 1 - SYSTEM ARCHITECTURE

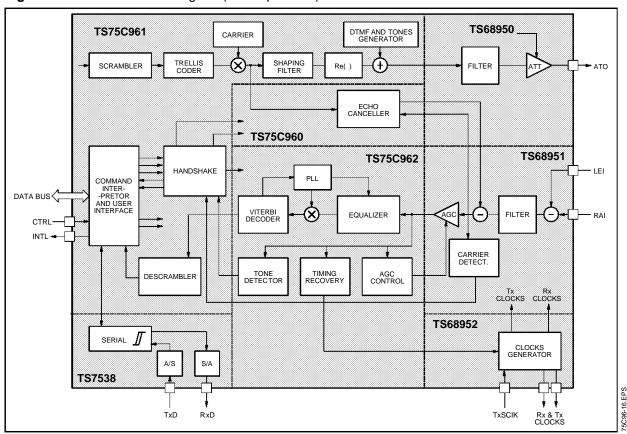

The SGS-THOMSON TS75C96 chip set is a highly integrated modem engine which provides the functionality and performance requirements for full-duplex 9600bps modem solutions at a low cost and with a small circuit area. At the heart of the modem engine are three SGS-THOMSON DSP's which implement the complete signal processing and control functions. The analog front end of the modem engine consists of the SGS-THOMSON MAFE three-chip set which is designed to meet the requirements of high-speed modem applications and particularly V.32 modems. An asynchronous to synchronous and synchronous to asynchronous converter provides serial data inputs and outputs. The only other components in the modem engine are the external RAM chips used for the far-end echo canceller delay line and the Viterbi decoder.

# 2 - PROCESSOR AND MAFE CHIPS ARRANGEMENT

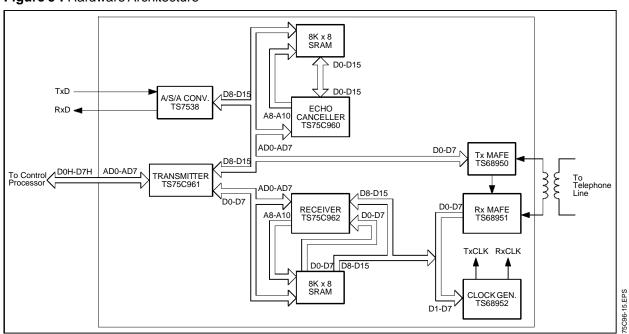

Figure 1 shows the interconnections between the MAFE signal processors and A/S – S/A converter. DSP# 1 (TS75C961) communicates with the con-

trol processor through its system bus, AD0-AD7. It is also connected to the two other DSP's and the TS7538 through its D0-D7 and D8-D15 data buses to transfer data, to pass a control command to the DSPs and to get the modem operation status and then pass it to the control processor. The transmitter, V.32 handshake and part of the receiver algorithms are implemented in this processor. DSP 0 implements the echo cancellation function. 4Kx16 of RAM are connected to this processor to implement the data delay line for the far end echo cancellation. DSP 2 implements most of the receiver functions. 2Kx16 of RAM are attached to it due to the requirements of the Viterbi decoder. The transmitter interface chip, TS68950 (see ref 5 of Appendix D), is connected to the 8 MSB's of the DSP 1 data bus. The echo replica is sent from DSP 1 to TS68950 then to the receiver interface chip, TS68951 (see ref 6 of Appendix D), after conversion to analog format. This chip and the clock generator chip, TS68952 (see ref 7 of Appendix D), are connected to the 8 MSB's of the DSP 2 data bus. The clock generator chip generates the A/D and D/A sampling clocks and the data bit and

baud rate clocks.

Figure 6: Functional Block Diagram (V.32 Operation)

#### 3 - OPERATION

#### 3.1 - Modes

The modem implementation is fully compatible with many CCITT and Bell recommendations. It operates at different bit rates from 9600 to 300bps. In the 9600bps mode, the trellis encoder and the Viterbi decoder can be switched in or out. Both the bit rate and trellis options are determined during the initial modem handshake sequence.

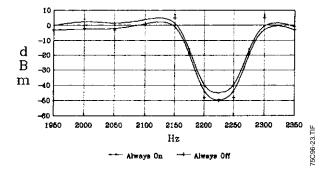

#### 3.2 - Signal Spectrum Shaping

A square root of 12.5 percent roll-off raised cosine filter is implemented in the transmitter to properly shape the transmit signal pulse. This filter is chosen based on a compromise of two considerations.

First, the signal should have a narrow spectrum to avoid severe distortion on the telephone line.

Second, the signal spectrum should be made as wide as possible to facilitate timing recovery in receiver.

#### 3.3 - Echo Cancellation

The echo canceller is implemented on a single DSP with its associated external RAM. It cancels both near-end and far-end echoes even in the presence of frequency offset in the far-end echo path. The near-end echo cancellation is better than 55dB and the residual near-end echo is smaller than - 65dBm with a near-end echo level of -10dBm at the receiver input and a far-end signal level of - 43dBm.

The combined near-end and far-end echo cancellers maintain the residual echo level 24dB below the received signal even if the far-end echo signal path introduces up to 10Hz of frequency offset. This level of cancellation is achieved when the far-end echo is 8dB below the received far-end signal.

#### 3.4 - Receiver Description

The incoming signal is sent to the receiver interface chip to have the echo removed before being sent to DSP 2. The timing recovery algorithm takes the signal after the echo cancellation to derive the timing error to control the sampling phase of the A/D. It is able to cope with distant modem frequency drifts up to  $1.10^{-4}$  as per CCITT rec. The A/D output samples are sent to the adaptive equalizer and the signal energy estimator for the gain control. The adaptive equalizer outputs a complex number every baud interval, which is then phase corrected by the carrier recovery loop. The Viterbi decoder makes hard decisions on the phase corrected samples for the adaptation of the equalizer and carrier recovery. It also makes soft decisions with an optimum decoding depth.

## 3.5 - Equalization

The modem receiver has a passband 26 bauds wide T/3 fractionally spaced automatic adaptive equalizer which can compensate for the signal degradation caused by low quality line conditions. The modem transmitter has a fixed compromise equalizer.

## 3.6 - Clock and Data Synchronization

Both transmit and receive clocks have the same nominal frequency value.

In fax modes, the transmit conversion clock signal (TxCCLK) is always set to 7200Hz, the transmit band clock signal (TxRCLK) is always set to 2400Hz.

Except in FSK modes, these clocks are plesiochronous. The nominal frequencies are :

| Mode      | TxCLK | TxRCLK | Byte/Irq | Rate             |

|-----------|-------|--------|----------|------------------|

| V.32TCM   | 9.6K  | 2.4K   | 1/2      | 9600bps Treillis |

| V.32QAM   | 9.6K  | 2.4K   | 1/2      | 9600bps QAM      |

| V.32QAM   | 4.8K  | 2.4K   | 1/4      | 4800bps          |

| V.29      | 9.6K  | 2.4K   | 1/2      | 9600bps          |

| V.29      | 7.2K  | 2.4K   | 3/8      | 7200bps          |

| V.29      | 4.8K  | 2.4k   | 1/4      | 4800bps          |

| V.27ter   | 4.8K  | 2.4K   | 1/4      | 4800bps          |

| V.27ter   | 2.4K  | 2.4K   | 1/8      | 2400bps          |

| V.22bis   | 2.4K  | 0.6K   | 1/8      | 2400bps          |

| V.22      | 1.2K  | 0.6K   | 1/16     | 1200bps          |

| V.22      | 0.6K  | 0.6K   | 1/32     | 600bps           |

| Bell 212A | 1.2K  | 0.6K   | 1/16     | 1200bps          |

| V.23      | 7.2K  | 1.2K   | 3/8      | 1200/75bps       |

| Bell 103  | 7.2K  | 1.2K   | 3/8      | 300bps           |

| V.21      | 7.2K  | 1.2K   | 3/8      | 300bps           |

Figure 7: Clock Signals for Synchronous Transmission

The TxCCLK is always 7.2kHz. The TxRCLX is always 2.4kHz.

The TxMCLK is always set to 2.4kHz after a configuration command CV32, CV22B.

During the hansdshake (V.32 and V.22bis) the bit clock (TxCLK and RxCLK) is set to the maximum value (respectively 9600Hz and 240Hz). At the end of the handshake, depending of the negociation, this frequency is automatically set to the proper value.

#### 3.7 - Tone Generator

The TS75C96 has thirteen tone commands to quickly program the tone generators to generate the 2100Hz Answer Tone (ANSWR) and the tone pairs for DTMF digits (DTMF0, ..., DTMF9, DTMF\*, DTMF#). These commands provide the tones and control required for normal operation of the modem, but do not enable tone generation.

Some circumstances might arise where additional tones are desired. For such cases, the TS75C96 provides the user with the ability to generate such additional tones. This special feature is achieved through use of the tone control commands.

The TS75C96 maintains a pair of locations which are reserved for tone generation parameters. These locations are denoted as TONE1 and TONE2. These locations may be programmed by the use of the define tone commands, DEFT1 and DEFT2. These commands provide the two tone generators with the phase increment of the tone to be generated with respect to the 7200Hz sample rate. (\$7FFF = +180°).

The normal tone commands automatically program the tone generators. The DEFT1 and DEFT2 commands do not change the enabled or disabled state of the tone generators. If a tone is being generated when the DEFT command is received, the new tone will be generated without further action. If tone generation was not in progress it is not started.

Enabling the tone generators is accomplished by the tone control commands TGEN0, TGEN1, TGEN2, and TGEN12. Each of these commands affects both tone generators. TGEN0 disables both tone generators and TGEN12 enables both tone generators. To enable tone generator 1 and disable tone generator 2 the TGEN1 command is used. For the reverse condition, with generator 1 disabled and generator 2 enabled, the TGEN2 command is employed.

Refer to the command in appendix A for more detailed information.

Generation of special user tones is not part of the normal data communications operations of the mo-

dem. Use of this feature may interfere with data transfer operations. It is the responsability of the user to insure that the tone generators are used at a time when such interference will not occur and to disable both tone generators when the tone generation operations have been completed.

#### 3.8 - Test Modes

The modem can be configured in two test modes, namely analog loop back and digital loop back modes. These loop back modes conform to the test loops 3 and 2 respectively defined in CCITT recommendation V.54.

In the local analog loop back mode, the transmitter signal is directly fed back into the local receiver input with the echo canceller enabled. The user is responsible for supplying a switch, which is controllable by the control processor, to enable or disable the analog loop back mode. The receiver descrambler is set as the inverse of the transmitter scrambler so that the receiver detects correct bits.

In all fax modes of operation, the TS75C96 supports the analog loop back capability. The command sequence is :

- CFAX to initialize FAX speed and parameter.

- SYNC to enable the receiver to demodulate FAX signal.

- HSHK to start FAX handshake (H status bit goes high).

When the H bit goes low, the TS75C96 can transmit and demodulate the incoming bit stream.

When using PLCC packages, a low power pin allows to drastically reduce the power consumption of the DSP's. The output clock frequency is divided by 16. The low power mode is disabled by a hardware reset on the 3 DSP's.

#### 3.9 - Power-on Initialization

When the power is turned on, the transmitter interface sets the output signal attenuation to infinite. This avoids undesirable signal transmission on the telephone line (see ref 5 of Appendix D). The gain of the AGC in the receive interface is set at the lowest level to avoid signal clipping during the initial handshake. The clock generator is programmed to generate all the necessary clocks for the 9600bps mode. The clocks include the 7200Hz sampling clock, the 2400Hz baud rate clocks and the 9600bps bit rate clocks. The transmit clocks are free running when the TxSCLK pin is tied to a fixed logic level. Otherwise, the transmit bit clock is synchronized to the frequency present at the TxSCLK pin. DSP 1 is configured properly to receive commands from the control processor.

#### 4 - MODEM INTERFACE (Figure 4)

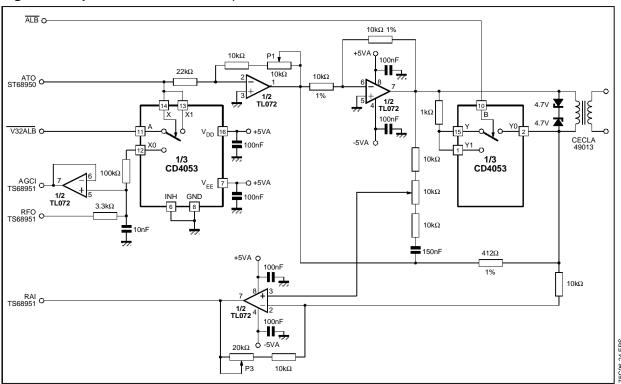

## 4.1 - Analog Interface

The transmit signal at the tip and ring is programmable over a 22dB dynamic range by 2dB steps in TS68950. The signal level can be further scaled to any value by setting a scaling factor in the DSP. The nominal Transmit level, at the ATO pin is -5.7dBm in V.32.

#### 4.2 - Digital Interface

The DSP and control processor interface complies with the system bus interface of the ST18930. The interface to the control processor is managed by DSP 1 as shown in Figure 5. The DSP signals which are presented to the interface, and a brief definition of the signals are tabulated in Table 1.

All information exchanges across this interface conform to the three byte mailbox structure (see ref 4 of Appendix D) and protocol of the DSP. As may be seen in the table, the DSP generates a control signal, INTL, which defines the mailbox handshake operation.

## 4.2 - V.24 Data Interface

The TS75C96 provides two different modes for data transfer:

- Serial V.14 interface synchronous or asynchronous.

- Parallel 8bit synchronous interface.

Figure 8: Functional Interconnect Diagram

| TXD RXD RXCLK RXD RXRCLK TXMCLK TXMCLK TXMCLK TXCLK RXMCLK TXCLK RXMCLK TXCLK RXMCLK TXCLK RXMCLK TXCLK RXMCLK RXM |              | 1        | iai iritercom |           |                  |                 |             |        |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|---------------|-----------|------------------|-----------------|-------------|--------|-------------------|

| TXSCLK TXMCLK TXCLK TXCLK TXCLK TXCLK TXCLK TXCLK TXCLK TXCLK RXMCLK TXCLK TXC | TxD          |          |               | <b></b>   | :D               | TxRCLK 🖵——      | ►           |        |                   |

| TXCLK  TXCLK  RXMCLK  TXCLK  RXMCLK  TXCLK  RXMCLK  TXCLK  RXCLK  RXMCLK  RXMC | RxD          | <b>-</b> | <b> </b>      | R:        | dD I             | RxRCLK 🖵—       | <b>&gt;</b> |        |                   |

| TILEPHONE  INTERFACE  HOST PROCESSOR  RWL  AGND  POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113          |          | <u> </u>      | <b>──</b> | SCLK             | TxMCLK 🕂—       | ►           |        |                   |

| PROCESSOR POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 114          | -        |               | тъ        | CLK F            | RxMCLK —        | ►           |        |                   |

| PROCESSOR POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 비 비 115      | -        | 1             | R         | CLK              |                 |             |        |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V.24 INTERFA |          |               | C:        | TS75C9 SL OSL WL | 6 RAI +5VA AGND | POWE        | ACE FR | TELEPHONE<br>LINE |

Table 1: Digital Interface Signals

| Interface Signals                                     | Signal Definition                                                                                                                                                         |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0H<br>D1H<br>D2H<br>D3H<br>D4H<br>D5H<br>D6H<br>D7H  | Data Bus (LSB) Data Bus                                                                  |

| RWL<br>SDSL<br>INTL<br>CSL<br>RSL                     | Write System Data Strobe Interrupt Request Mailbox Handshake DSP Select                                                                                                   |

| TxD<br>RxD                                            | Transmit Data<br>Receive Data                                                                                                                                             |

| TxRCLK TxRCLK TxCLK RxCLK TxMCLK TxMCLK RxMCLK TxSCLK | Transmit Baud Rate Clock Receive Baude Rate Clock Transmit Bit Rate Clock Receive Bit Rate Clock Transmit Multiplex Clock Receive Multiplex Clock Transmit Terminal Clock |

The mode of operation is selected using the SE-RIAL command of the CCI (Control Command Interpreter). The TS75C96 does also include dedicated hardware (scramblers and detectors) to detect all the V.54 specific signals.

#### 4.3 - Memories Interface

DSP0 and DSP2 require external static RAM Memory. A minimum of 2Kx16 is required by DSP2 for Virterbi decoding and 4Kx16 by DSP0 for echo cancellation. The maximum access time to allow proper operation is 100ns for both memories. The use of 8Kx8 Static RAM from SGS-THOMSON is recommended. However DSP0 allows use of different type of memory. When using 8Kx8 memory pin BS0 of DSP0 must be tied to +5V otherwise tied to ground. (Intel or Motorola bus choice)

## 4.4 - Control Processor/DSP Interface

As seen by the software in the user provided control processor, DSP 1 is a synchronous machine. It requires the attention of the control processor at regular intervals in order to perform properly. Any failure of the control processor to interact with the modem engine in a timely manner will result in reduced performance or improper operation.

Each interaction begins when the control processor sends a three byte command to the mailbox. Once the command has been written to the mailbox, the ownership of the mailbox is relinquished by the control processor. Upon acquisition of the mailbox, DSP 1 reads the command bytes and then sends a three byte response to the mailbox. Then, DSP 1 relinquishes the ownership of the mailbox back to the control processor. The received command is then decoded and the embedded data and/or operational parameters are extracted and acted upon as appropriate. The modem status information will be collected for the next mailbox exchange. The control processor handles the returned information as soon as it regains the ownership of the mailbox.

Because the control processor owns the mailbox initially, it may store a command at any time before it is required by DSP 1. After this, the mailbox becomes available to DSP1 and can be read by it when required. The rate of exchange beetwen the TS75C96 mailbox and the control processor is nominally 2400 interrupts per second. However, this rate can be reduced down to 20 interrupts per second when using the SERIAL command. If the collected status information does not induce any specific command from the last, then a NOP command must be sent to ensure proper operation

#### 4.5 - Mailbox Description

The mailbox located internally to the DSP contains 3-byte input (RIN) and 3-byte output (ROUT) shift registers.

The DSP has an internal flag RDYOIN which indicates whether the DSP (RDYOIN = 0) or control processor (RDYOIN = 1) has access to the mail-box.

The DSP can relinquish its accessability to the mailbox by setting RDYOIN but it can no longer regain access to the mailbox as RDYOIN is reset only after the control processor relinquishes its accessability to the mailbox.

The access protocol and system bus transfers are controlled by an internal I/O sequencer within the DSP described as follows:

- The mailbox is made available to the control processor by the DSP program which sets RDYOIN flag to 1. This action will cause INTL mailbox handshake signal to switch to the active (low) state.

- The control processor detects INTL active and dummy reads the mailbox by forcing DSP Select (CSL) and Register Select (RSL) low along with write signal (RWL) high. The activated Data Strobe signal (SDSL = 0) validates the above signals.

- 3. The DSP detects the dummy read of its mailbox via the control signals mentioned in 2 and negates INTL mailbox handshake signal within 800ns.

- The control processor detects the negation of INTL indicating that the DSP mailbox is available for data transfers. The control processor writes three 8-bit bytes and reads three 8-bit bytes in the mailbox shift registers RIN, ROUT respectively.

- 5. The exchange protocol described above is terminated by the control processor performing a dummy read of the mailbox as in 2 but with RSL in the high state.

- The RDYOIN flag within the DSP is cleared to 0 by the dummy read of the mailbox in step 5 and the DSP now has access to RIN and ROUT registers within the mailbox.

#### **USER INTERFACE - COMMAND SET**

The command set has the following attractive features:

- User friendly with easy to remember mnemonics.

- Allows straightforward expansion with new commands to suit specific customization requirements.

- Fully compatible with other SGS-THOMSON DSP-based modem products.

The command set has been designed to provide the necessary functional control of the TS75C96. Each command falls into one of several groups, based on function and the presence or absence of parameters. The length of the OP code varies with instruction type, but in all cases, a command consists of three bytes. If no specific command is necessary to drive the TS75C96, a NOP command must be sent to the mailbox. The commands which pass parameters or data to DSP 1 have a short OP code format. Byte 0 forms the OP code portion of the command. Bytes 1 and 2 are data and/or parameters associated with each OP code. The meaning of the last two bytes is dependent on the specific instruction. Other instructions command the TS75C96 to perform certain specific tasks. These do not pass parameters or data to the TS75C96. These commands have an OP code which is a full 24 bits in length. When a command requires an answer from DSP#1, the control processor has to wait until the answer has been received before issuing a new command requiring an answer. Howewer, the control processor can still send commands which do not require an answer. The command set of the TS75C96 is summarized below. The descriptions are of the form:

#### **MNEMONIC** (OPCODE): DESCRIPTION

For detailed information and data format specifics of each command, please refer to appendix A.

#### 1 - COMMAND SUMMARY

#### 1.1 - Operational Control Commands

**FREZ** (16,17,1B,1C): Freezes adaptive processes.

**HSHK** (040000): Handshake. Begins the handshake sequence. The TS75C96 carries out all the steps defined in the CCITT recommendation. The status reported to the control processor will indicate the success or failure of the process and its progress.

**INIT** (0600C0): Initialize. Initialize the modem. Set all parameters to default values and wait for commands for the control processor.

NOP (000000): No Operation. No new operation

is commanded. The state of the TS75C96 remains unaltered and a previously invoked multi-baud command (such as HSHK) continues.

RTRA (050000): Retrain. Start sending the retrain sequence as defined in the CCITT recommendation.

**SCRM** (18): Enable /disable the V.22bis transmit scrambler. At the end of a handshake, both scramblers are enabled. The purpose of this command is for the use in loop 2 configurations (Digital loopback). During normal transmission mode this command must not be used.

**SETGN** (02): Set Gain. This command sets a global gain factor, which will be multiplied by all transmit samples before being sent to the TS68950. Bytes 1 and 2 store the gain factor.

**SYNC** (1A): Start fax receiver synchronization.

**STOP** (19): Stop fax transmitter according with CCITT V.27ter.

#### 1.2 - Data Communications Commands

XMIT(01): Transmit data.

**SERIAL**(15): Enables the use of the TS7538. Using it informs the TS75C96 that it must get/send Bytes of data from/to the TS7538. When this mode is enabled, one must not use the XMIT command. To return to parallel synchronous mode (For V.22bis digital loopback handshake, for example) one must first disable the SERIAL mode (SERIAL,0,0). When enabled, the serial mode allows the reduction of the frequency of the IRQ signal. This period can be reduced down to 100ms.

Warning: the status word of the modem, furnished by the TS75C96, is updated by the mailbox exchange. Even if the microcontroller does not want to send a specific command, it must not program the IRQ rate to a value which inhibits overall modem performance. The serial command allows the programming of the TS7538.

Changing the CR0 and CR1 register values of the TS7538, when in data mode, can cause a loss of data.

#### 1.3 - Memory Manipulation Commands

**SPAC** (13): Store Parameter And Count. Store parameter in addressed memory and increment the pointer. This command passes data in bytes 1 and 2, least significant byte in byte 1. It is used to write an arbitrary 16-bit value into the writable memory location currently specified by the Memory Address Register. The contents of the Memory Address Register are incremented by 1 at the completion of this command.

**SPAM** (12): Store Parameter in Addressed Memory. This command passes data in bytes 1 and 2, least significant byte in byte 1. It is used to write an arbitrary 16-bit value into the writable memory location currently specified by the Memory Address Register.

WARP (10): Write Address and Return Parameter. This command allows the controller to read any of the XRAM, YRAM, ERAM or CROM (DSP internal or external memory areas) of any of the three modem DSPs without interrupting the processors. The address to the V.32 modem engine is provided in bytes 1 and 2 of the command (least significant byte first). DSP# 1 stores the address in the Memory Address Register and returns the contents of the addressed location.

WARPX (11): Write Address and Return Parameter Complex. The address to the V.32 modem engine is provided in bytes 1 and 2 of the command (least significant byte first). DSP 1 stores the address in the Memory Address Register. The most significant bytes of the real and imaginary parts of a complex number are returned. The 8 most significant bits of the data addressed by the Memory Address Register are returned to the control processor through byte 1. Byte 2 stores the 8 most significant bits of the data at the location immediately higher. The Memory Address Register retains the address provided. (i.e. it is not incremented).

#### 1.4 - Configuration Control Commands

**CV32** (20): Configure modem for V.32. Configure the modem as Originate / Answer, 9600/4800, Viterbi / No-Viterbi, Analog Loopback.

**CFSK** (1D): Configure modem for FSK modes of operation (V.23/V.21/Bell 103).

**CFAX** (1F): Configure for Fax modes. (V.29/V.27ter)

**CV22B** (1E) : Configure modem for V.22bis/V.22/Bell212A modes.

## 1.5 - Mafe Manipulation Commands

**CMAFE** (07): Configure MAFE. The following two bytes of this command are written directly to the MAFE chip set (TS68950/1/2).

RRR1 (080000): Read Register 1. Causes the

TS75C96 to read the 12 bit contents of the MAFE register RR1.

RRR2 (090000): Read Register 2. Causes the TS75C96 to read the 12 bit contents of the MAFE register RR2.

**WTR1** (0A): Write Register 1. Causes the TS75C96 to write the supplied data to the MAFE register TR1.

**WTR2** (0B): Write Register 2. Causes the TS75C96 to write the supplied data to the MAFE register TR2.

#### 1.6 - Tone Select Commands

**TONE** (0C): Select Tone. Program the tone generator(s) for the desired tone(s). Examples include:

**ANSWR** (0C1000): Program the tone generator for the 2100Hz answer tone.

**DTMF** (see appendix): Program the tone gene-rators for the tone pair which forms the specified DTMF digit.

This command selects the tones to be transmitted, but does not enable the tone generators. To transmit the tones, the TONE control commands must be issued.

## 1.7 - Tone Control Commands

**DEFT1** (0E): Define Tone 1. Define tone 1 as specified by the parameter provided. The two data bytes following the opcode are used to program, but not enable, tone generator 1. The data for the tone is represented as a phase offset per sample. Byte 1 stores the least significant byte of the phase increment. (+ 180° = \$7FFF)

**DEFT2** (0F): Define Tone 2. Define tone 2 as specified by the parameter provided. The two data bytes following the opcode are used to program, but not enable, tone generator 2. The data for the tone is represented as a phase offset per sample. Byte 1 stores the least significant byte of the phase increment.

**TGEN** (0D): Tone Generator control. Enable or disable tone generator 1 and tone generator 2 according to parameter provided. If both tone generators are enabled, the level of tone 2 is 2dB higher than that of tone 1.

#### 2 - STATUS REPORTING

Whenever DSP 1 owns the mailbox, it transmits the modem status to the control processor. The status consists of three bytes of information which are stored by DSP 1 in its ROUT register for access by the control processor. At each mailbox exchange a set of 3 bytes is returned to the microcontroller. Three type of information can be given to the host processor. The order of priority is:

- 1. Bytes of received data.

- 2. Answer to a Command.

- 3. The status of TS75C96, including RS232 circuits, signal quality information, multiple tone detector flags. Bits D4, D3 of byte 0 of the status word select the type of data contained in the current status word. Data are available both in parallel and serial mode unless the user makes the choice of reducing the IRQ rate. Data bits have higher priority than the answer to the previous command. If both data byte and command answer are ready to be sent, the data will be sent. The TS75C96 supports 3 different phases to which correspond 3 different possibilities of status words.

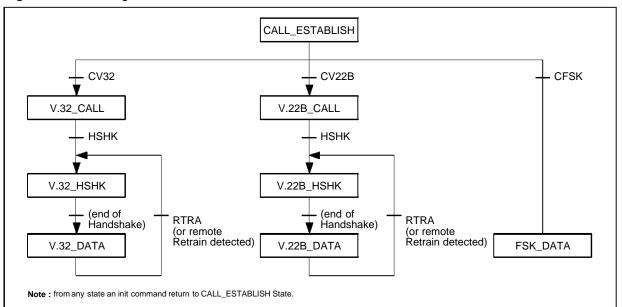

- At the beginning (master reset or INIT command) the TS75C96 is in a state called CALL ESTABLISHMENT mode. The user is establishing a call and is waiting for an answer from the far end modem.

- After that state, the hanshake with the far end modem is started using the HSHK command (associated with one of the CV32, CV22B commands). The state of the TS75C96 becomes HANDSHAKE.

- 3. At the end of the handshake, the TS75C96 goes into the DATA TRANSFER mode. At that step, bytes of data can be exchanged with the far end modem. When the TS75C96 detects a far end retrain, or when the host processor sends a RTRA command, the TS75C96 goes back into the HANDSHAKE mode. The bit D1 of status Byte indicates that the TS75C96 is in HANDSHAKE mode.

Byte 0 contains status flags. Refer to appendix B for the detailed format of the status response. The four most significant bits, F00, F01, F10 and F11, indicate various conditions during the call establishment, handshaking and the data modes. They

have different meanings in different modes. The flag DAV1 and DAV2 are used to indicate the type of information contained in bytes 1 and 2. Bit H is used to indicate the condition of the handshake and bit 107 informs the control processor whether the 107 flag has to be set.

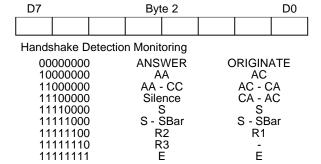

DAV1 and DAV2. If both DAV1 and DAV2 are set to 1, bytes 1 and 2 contain the data in response to the previous command. Refer to the relevant commands in appendix A to get the detailed information on the interpretation of the data in bytes 1 and 2. Otherwise, they contain either the received data bits or the handshake detection status or both.

The least significant bit is the first bit received. The data bits are stored in byte 1 when DAV2 is 1 and DAV1 is 0. When DAV1 is 1 and DAV2 is 0, the control processor should ignore the data in byte 1 and get the detection status from byte 2. During handshake operations the TS75C96 reports the detection status regularly. When the rate sequence is received, it will be transferred in byte 1 of the response. Each bit in byte 2 indicates the detection of a specific event in the training sequence. It has different meanings for call and answer modems. For detailed information, refer to appendix B. During the data mode, byte 2 is always provided, but is used only when there are two bytes of data to transmit.

F00-F11 bits. During the call establishment operation, the TS75C96 reports call progress tones through the F01 and F00 flags. F00 is set to 1 when the signal energy in frequency band 1 is above the threshold level. F01 is set to 1 when the signal energy in band 2 is above the threshold level. Detection of the 2100Hz or 2225Hz answer tone is indicated by setting the F10 flag to a 1. During handshake operations, all four bits are used to indicate the line condition and some detection results. F01 is set to 1 if any segment in the training sequence is not detected within a time out. This bit can be used to indicate a non V.32 detection if either AA is not detected in the answer modem or the AC is not detected in the call modem. Both F00 and F01 are set to 1 when an illegal mode or a GSTN cleardown is received in the rate sequence. The detection of the rate sequence is reported in the flags F11 and F10. When the modem is operating at 9600 bps without trellis coding, these bits are both set to 0. With trellis coding at 9600bps, F11 is set to 1 and F10 is cleared to 0. For 4800bps, 0 and 1 will be placed in F11 and F10, respectively.

During data mode, the perceived line quality is reported in the flags F01 and F00. The line conditions are reported as either good (code 00), poor (code 01), or terrible (code 10). The code 10 should be interpreted as a local modem retrain request. Upon receipt of this code, the controller can issue the RTRA command to begin the retrain procedure. The code 11 is used when the remote modem begins a retrain sequence. The control processor is then responsible for manipulating the appropriate data communications interface signals.

H and 107 bits. When the TS75C96 is required to perform the CCITT handshake sequence, the H bit is set to 1 for the duration of the handshake. At the successful completion of the handshake operation the H flag will go to 0 and the control processor is then responsible for manipulating the appropriate data communications interface signals. e.g. 106 and 109.

The 107 flag is set to 1 to indicate that the controller should assert signal 107 on the data communication interface.

In FAX mode, the H bit can indicate a handshake in progress, either in the transmit path (transmitting segment 1 to 5 or A to B), or in the receiver.

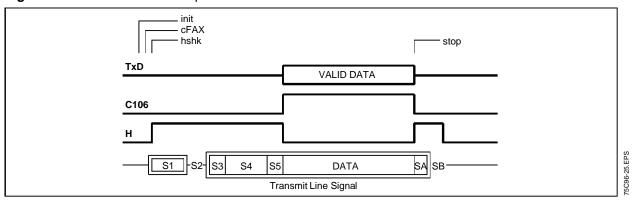

#### C106, Clear To Send.

Tells the transmit section that the modem can sends bits of data. The bit stream of data can come from the TS7538 when the serial mode is enabled, or directly from the microcontroller in parallel mode.

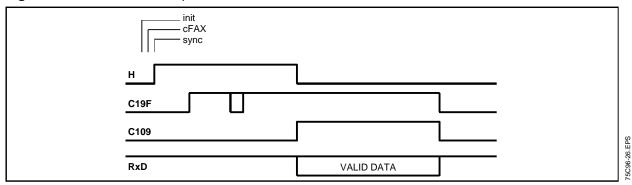

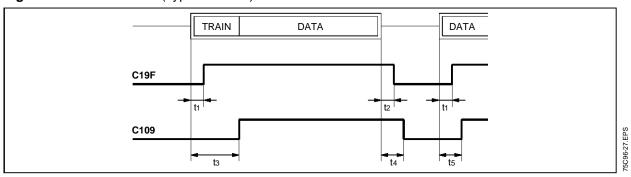

#### C19F, Fast Carrier Detect.

Tells the receive section that a signal is present in the line. The threshold for detection is equal to the high level of the regular carrier detect.

## C109, Carrier Detect.

Tells the receive section that a coherent V.29/V.27ter signal is present on the line. The high level for detection is set by default to -43dBm, the low level to -48dBm, the minimum hysteresis is 2dB. This signal is also used internally to clamp outgoing received data.

#### 3 - COMMAND LIST

#### **Operational Control Commands**

| Command<br>Mnemonic | OP Code (HEX) | Description                                |

|---------------------|---------------|--------------------------------------------|

| UFZEC               | 170000        | UnFreeZe Echo Canceller                    |

| FREZQ               | 1B0000        | FREeZe the EQualizer adaptation            |

| FRELC               | 160000        | FREeZe the Echo Canceller adaptation       |

| UFZEQ               | 1C0000        | UnFreZe EQualizer .                        |

| HSHK                | 040000        | HandSHaKe with Other Modem                 |

| INIT                | 0600C0        | NITialize modem                            |

| NOP                 | 000000        | No OPeration                               |

| RTRA                | 050000        | ReTRAin                                    |

| SCRM                | 18            | Enable / Disable V.22bis SCRambler         |

| SETGN               | 02            | SET the scaling factor for the transmitter |

| STOP                | 19            | Stop FAX Transmitter                       |

| SYNC                | 1A            | Start FAX Receiver Synchronization         |

## **Data Communication Commands**

| Command<br>Mnemonic | OP Code (HEX) | Description                                                                                         |

|---------------------|---------------|-----------------------------------------------------------------------------------------------------|

| XMIT<br>SERIAL      | 01<br>15      | Transmit Data and Initiate Additional Transfer (in parallel data mode) Transmit Data in SERIAL mode |

#### **MAFE Communication Commands**

| Command<br>Mnemonic                   | OP Code (HEX)                      | Description                                                                                      |

|---------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|

| CMAFE<br>RRR1<br>RRR2<br>WTR1<br>WTR2 | 07<br>080000<br>090000<br>0A<br>0B | Configure MAFE Chipset Read Mafe Reg RR1 Read Mafe Reg RR2 Write MAFE Reg TR1 Write MAFE Reg TR2 |

## **TONE Select Commands**

| Command<br>Mnemonic | OP Code (HEX) | Description               |

|---------------------|---------------|---------------------------|

| ANSW                | 0C1000        | Select 2100Hz ANSWeR Tone |

| DTMF0               | 0C0000        | Select DTMF Digit 0       |

| DTMF1               | 0C0100        | Select DTMF Digit 1       |

| DTMF2               | 0C0200        | Select DTMF Digit 2       |

| DTMF3               | 0C0300        | Select DTMF Digit 3       |

| DTMF4               | 0C0400        | Select DTMF Digit 4       |

| DTMF5               | 0C0500        | Select DTMF Digit 5       |

| DTMF6               | 0C0600        | Select DTMF Digit 6       |

| DTMF7               | 0C0700        | Select DTMF Digit 7       |

| DTMF8               | 0C0800        | Select DTMF Digit 8       |

| DTMF9               | 0C0900        | Select DTMF Digit 9       |

| DTMF*               | 0C0E00        | Select DTMF Digit *       |

| DTMF#               | 0C0F00        | Select DTMF Digit #       |

| TONE                | 0C            | Select TONE(s)            |

## **Configuration Control Commands**

| Command<br>Mnemonic | OP Code (HEX) | Description                                                                              |

|---------------------|---------------|------------------------------------------------------------------------------------------|

| CV32<br>CFAX        | 20<br>1F      | Configure Modem for V.32<br>Configure for FAX modes (V.29/V.27ter)                       |

| CFSK<br>CV22B       | 1D<br>1E      | Configure Modem for FSK (V.23/V.21/Bell 103) Configure Modem for V.22/V.22bis/ Bell 212A |

## **Memory Manipulation Commands**

| Command<br>Mnemonic           | OP Code (HEX)        | Description                                                                                                              |

|-------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|

| SPAC<br>SPAM<br>WARP<br>WARPX | 13<br>12<br>10<br>11 | Write MEM and Increment MEM Pointer Write MEM Write MEM and Pointer & Read MEM Write MEM and Pointer & Read MEM & MEM +1 |

## **TONE Control Commands**

| Command<br>Mnemonic | OP Code (HEX) | Description                   |

|---------------------|---------------|-------------------------------|

| DEFT1               | 0E            | Define Tone 1                 |

| DEFT2               | 0F            | Define Tone 2                 |

| SLNT                | 0D0000        | Transmit no Tone              |

| TGEN0               | 0D0000        | Tone Generators Disabled      |

| TGEN1               | 0D0100        | Tone Generator 1 Enabled      |

| TGEN2               | 0D0200        | Tone Generator 2 Enabled      |

| TGEN12              | 0D0300        | Tone Generators 1 & 2 Enabled |

**APPENDIX A: COMMAND SET DESCRIPTION**

**CFAX** - Configure for FAX Modes

## **INSTRUCTION TYPE**

Configuration control command

## **OPCODE**

1F

## **SYNOPSIS**

CFAX mode al atn

#### **DESCRIPTION**

CFAX is used to select the FAX mode of operation.

## BYTE 0 DEFINITION (OP CODE)

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|

## **BYTE 1 DEFINITION**

| 0 | 0 | EP1 | EP0 | 0 | M2 | M1 | MO |

|---|---|-----|-----|---|----|----|----|

|   |   |     |     |   |    |    |    |

| BIT |     | DEF  | INITION      |                     |

|-----|-----|------|--------------|---------------------|

| EP1 | EP2 | Echo | o protectio  | n tone              |

| 0   | 0   | no e | cho protec   | tion tone           |

| 0   | 1   | Sho  | rt protectio | n tone 30ms         |

| 1   | 0   | Long | g echo prot  | tection tone 190ms  |

| M2  | M1  | MO   | FAX Mod      | e                   |

| 0   | 0   | 0    | V.29         | 9600bps             |

| 0   | 0   | 1    | V.29         | 7200bps             |

| 0   | 1   | 0    | V.29         | 4800bps             |

| 1   | 0   | 0    | V.27Ter      | 4800bps             |

| 1   | 0   | 1    | V.27Ter      | 2400bps             |

| 1   | 1   | 0    | V.27Ter      | 4800bps short train |

| 1   | 1   | 1    | V.27Ter      | 4800bps short train |

#### **BYTE 2 DEFINITION**

| ATN3 | ATN2 | ATN1 | ATN0 | 0 | 0 | LL | 0 |

|------|------|------|------|---|---|----|---|

BIT DEFINITION

ATN3... 0 Transmit Attenuation

LL Carrier Detect Level

0 PSTN (43dBm/-48dBm)

1 Leased line (33dBm/-38dBm)

# **CFSK** - Configure for FSK Modes

#### **INSTRUCTION TYPE**

Configuration control command

### **OPCODE**

1D

## **SYNOPSIS**

CFSK al orig atn mode II

#### **DESCRIPTION**

CFSK is used to select the FSK mode of operation.

## BYTE 0 DEFINITION (OP CODE)

| 0 |  | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

|---|--|---|---|---|---|---|---|---|

|---|--|---|---|---|---|---|---|---|

#### **BYTE 1 DEFINITION**

| 0   | 0 | 0 | 0 | AL    | MOD1  | MOD0 | ORIG |

|-----|---|---|---|-------|-------|------|------|

| DIT |   |   | \ | UITIC | \ N I |      |      |

| BIT  |     | DEFINITION                       |

|------|-----|----------------------------------|

| AL   | 0/1 | Analog loopback disabled/enabled |

| ORIG | 0/1 | Answer mode/Originate mode       |

| MOD1 |     | MOD0                             |

| 0    |     | 0 V.23                           |

| 0    |     | 1 V.21                           |

| 1    |     | 0 Bell 103                       |

#### **BYTE 2 DEFINITION**

| ATN3 | ATN2 | ATN1 | ATN0 | 0 | 0 | LL | 0 |

|------|------|------|------|---|---|----|---|

| BH     | DEFINITION                     |

|--------|--------------------------------|

| ATN3 0 | Transmit Attenuation (cF CV32) |

| LL     | Leased line carrier detect     |

| 0      | 43dBm/-48dBm                   |

33dBm/-38dBm

**CMAFE** - Configure the TS68950/1/2 components of the TS75C96

#### **INSTRUCTION TYPE**

MAFE manipulation command

## **OPCODE**

07

#### **SYNOPSIS**

CMAFE address register code data

#### **DESCRIPTION**

CMAFE is used to directly manipulate the operating parameters of the TS68950/1/2 components of the TS75C96. This is a low level command which allows the controller to alter such things as the transmit level, transmit timing, receive timing, and receiver parameters, etc. The command consists of a single byte OPcode followed by a byte containing the address code for the desired register and a data byte for the addressed register. The data bytes will be transferred in the order received and interpreted by the addressed device. Refer to the data sheets of the TS68950, TS68951, and TS68952 for programming specifics.

#### **BYTE DEFINITION (OP CODE)**

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|

#### **BYTE 1 DEFINITION**

| R | R | R | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

REG CODE (Refer to TS68950 Data Sheet).

#### **BYTE 2 DEFINITION**

DATA BYTE (Refer to TS68950 Data Sheet)

CV22B - Configure for CCITT V.22bis, CCITT V.22 and Bell 212A Modes

#### **INSTRUCTION TYPE**

Configuration control command

## **OPCODE**

1E

#### **SYNOPSIS**

CV22B al mode orig atn LL guard fallback

#### **DESCRIPTION**

CV22B is used to select the CCITT V.22bis mode of operation. Select also, depending of Mode bits, the V.22, V.22 600bps and the Bell 212A.

### BYTE 0 DEFINITION (OP CODE)

| 0 0 0 | 1 | 1 | 1 | 1 | 0 |

|-------|---|---|---|---|---|

|-------|---|---|---|---|---|

#### **BYTE 1 DEFINITION**

| G1 G0 0 0 AL MOD1 MOD0 ORIG |

|-----------------------------|

|-----------------------------|

| BIT    |      | DEFINITION                       |

|--------|------|----------------------------------|

| AL 0/1 |      | Analog loopback disabled/enabled |

| MOD1   | MOD0 | Select Mode                      |

| 0      | 0    | V.22bis 2400bps                  |

| 0      | 1    | V.22 1200bps                     |

| 1      | 0    | Bell 212A 1200bps                |

| 1      | 1    | V.22 600bps                      |

| ORIG ( | )/1  | Answer mode/Originate mode       |

| G1     | G2   | Guard tone selection             |

| 0      | 0    | No tone                          |

| 0      | 1    | 550Hz                            |

| 1      | 0    | 1800Hz                           |

|        |      |                                  |

## **BYTE 2 DEFINITION**

|  | ATN3 | ATN2 | ATN1 | ATN0 | 0 | 0 | LL | FB |  |

|--|------|------|------|------|---|---|----|----|--|

|--|------|------|------|------|---|---|----|----|--|

| BIT    | DEFINITION                     |

|--------|--------------------------------|

| ATN3-0 | Transmit Attenuation (cF CV32) |

| FB     | Fallback mode for V.22bis      |

| 0      | disabled                       |

| 1      | enabled                        |

| LL     | Leased line carrier detect     |

| 0      | 43dBm/-48dBm                   |

| 1      | 33dBm/-38dBm                   |

CV32 - Configure for V.32 Mode

## **INSTRUCTION TYPE**

Configuration control command

#### **OPCODE**

20

## **SYNOPSIS**

CV32 speed ec orig atn al fc

#### **DESCRIPTION**

CV32 is used to alter the operating parameters of the TS75C96. The passed parameters provide a two bit speed code (SP0 & SP1) which selects the desired baud rate. EC parameter explicitly turns on or off the echo canceller. If the TS75C96 is operating in the originate mode, the ORIG parameter must be set. When this parameter is not set, the TS75C96 is configured as an answer mode device. The AI parameter allows the user to select the analog loopback test conditions. The transmit attenuation level is selected by the ATN parameter. etc.

## BYTE 0 DEFINITION (OP CODE)

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

| U | 0 |   | U | 0 | 0 | U | U |

#### **BYTE 1 DEFINITION**

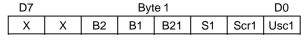

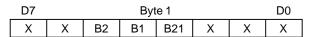

RSV RSV FC EC AL SP1 SP0 ORIG

Flag Bit Definition RSV - Reserved

FC 0/1 Do not/Do force cleardown EC 0/1 For end echo canceller off/on